What is a ROIC?

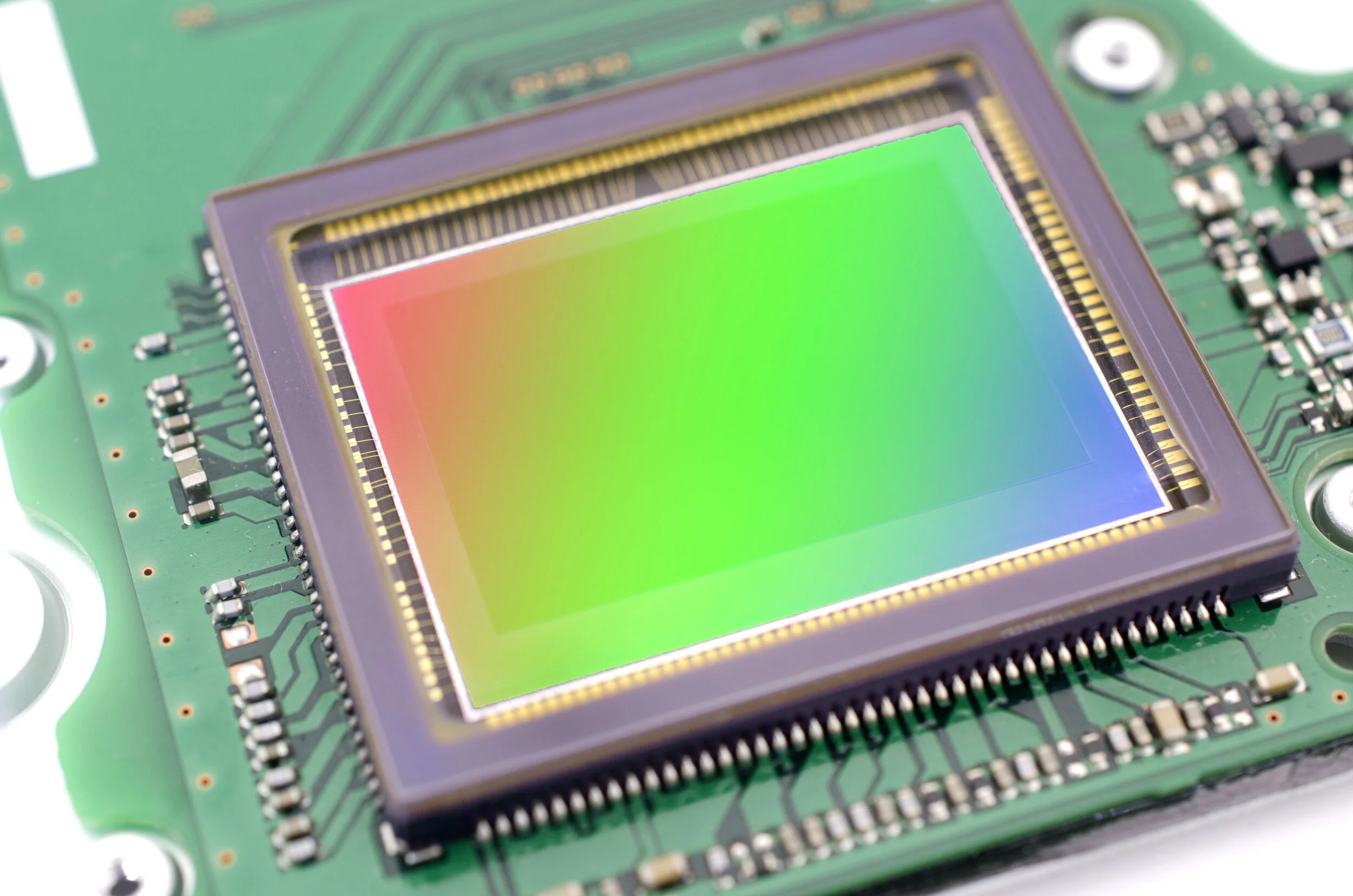

Readout Integrated Circuit (ROIC)

A Readout Integrated Circuit (ROIC) is a specialized microelectronic component designed to interface with sensor arrays, particularly in imaging and detection systems. In particle physics and similar fields, ROICs are commonly used with silicon strip detectors (SSDs). In such cases, the ICs are directly bonded to the silicon strip detectors, with the goal of achieving a channel pitch that closely matches the strip pitch, thereby minimizing the need for additional signal routing. When a particle strikes the silicon in the strip detector, it generates an electrical charge. The ROIC collects this charge and counts the number of events, effectively measuring how many particles have hit each strip.

The primary goal of the ROIC is to maximize signal gain while minimizing the readout noise, thereby optimizing the signal-to-noise ratio (SNR). Other key parameters that have to be optimized in the design include the maximum fluence the ROIC can handle without channel saturation, the uniformity of gain across all channels, the tolerance to sensor DC leakage, and the mitigation of excess noise due to the sensor’s capacitance presence. These are just some of the most common examples.

In the implementation of the IC, various types of signal processing can be implemented in the readout channel, including pulse preamplification, shaping, single or multiple thresholding, or even analog-to-digital conversion of the charge pulse amplitude. Different applications may require specific processing techniques to meet their needs.

ROICs are also utilized in hybrid sensors, where each channel is coupled to a pixel in a two-dimensional sensor array. This approach offers all the advantages of a photon-counting systems, while simplifying the system design and significantly increasing the readout channel density, allowing the system to handle very high fluxes. In these cases, ROICs enable the creation of fully functional imaging systems.

ISDI has designed many readout ICs (ROIC) for a number of applications. Here the most recent ones:

OPTIma: Readout ASIC for Strip Detectors

OPTIma is a charge sensitive device designed for 128-channel strips used in a proton path tracker. The ASIC is built as an asynchronous analogue frontend, capable of detecting the proton-generated charge and producing a pulse at the corresponding digital output.

The DAQ clock can be as fast as 125 MHz but the cyclotron facilities currently envisaged will have frequencies of 72 MHz and 106 MHz. A shaping time of about 4 ns is desired to improve the temporal resolution of the detection (this parameter is programmable up to 24ns). A Constant fraction discriminator (CFD) paired with a trigger comparator assure a timing resolution better than 500ps across the full energy range up to 100ke-.

A programmable threshold for the comparator determines the level at which each channel fires. The threshold has a 6-bit resolution and covers a 1000e- to 20ke- range in ~500 electron steps. Higher threshold ranges are available up to 250ke- via register setting.

RHEA: Rapid High Speed Extended ASIC.

Detector and RHEA aligned on the hybrid PCB and aluminium stiffener plate.

The PRaVDA collaboration has developed a solid-state imaging system for proton CT, utilizing silicon strip detectors. This system includes a tracking system that deduces individual proton trajectories through an imaging phantom, along with a Range Telescope (RT) that measures the residual energy (range) for each proto

ISDI designed the strip readout ASIC known as RHEA (Rapid High-speed Extended ASIC) for the project.

RHEA is a binary chip with 128 channels and a bonding pitch of 60μm, fabricated using a commercial 0.18μm CMOS technology. Each channel features two programmable thresholds: DAC1 ranges from 2000 to 10000 electrons, and DAC2 ranges from 20000 to 160000 electrons. The low threshold is utilized for noise rejection, while the high threshold allows for the detection of double hits per channel per readout cycle, which is more likely at higher fluences. Both thresholds have a 6-bit resolution and are fully programmable.

To accommodate high occupancy, the chip operates at a frequency of 104 MHz, with its front-end amplifier having a shaping time of 30 ns. This corresponds to four times the average cyclotron frequency for the energy range of interest (60–200 MeV) at the facilities that will be used.

RHEA will produce 7-bit addresses of all strips hit for a particular proton pulse. The ASIC is read out at a frequency of 26MHz and up to 4 channels can be read out per readout cycle (39 ns). More channels can be read out at the expense of event loss (channel gating) extending the readout over multiple cycles.

Both the PRaVDA trackers and the RT are based on SSDs. SSDs were made of 150μm-thick n-in-p silicon with an active area of 93 × 96 mm2 and a strip pitch of 90.8 μm. Each detector contains 2048 strips (channels) and is read out by 16 custom ASICs located on both sides of the sensor.

ISDI’s Image Sensor team, based in London and Austria can help you optimise the design your next detector by using one of our innovative readout designs, radiation hardened pixel design, ADCs or custom design services.

PCB viewed through a microscope